- ISBN:9787121464096

- 装帧:平塑勒

- 册数:暂无

- 重量:暂无

- 开本:其他

- 页数:240

- 出版时间:2023-11-01

- 条形码:9787121464096 ; 978-7-121-46409-6

本书特色

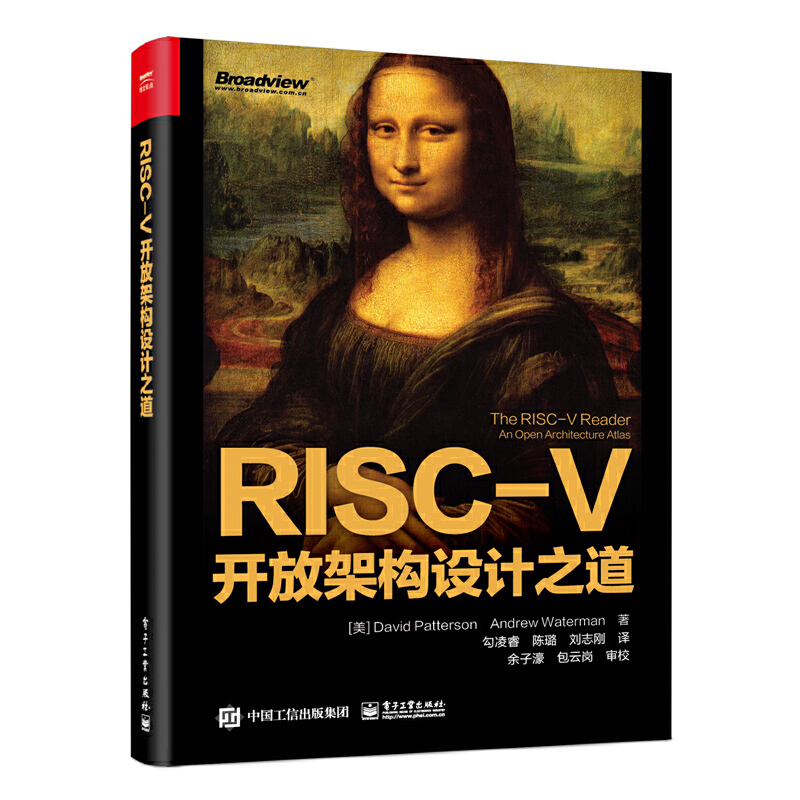

《RISC-V开放架构设计之道》由RISC-V架构的作者、著名的计算机体系架构专家David Patterson亲自主笔撰写, 以*精简的笔墨,清晰、透彻地勾勒了RISC-V架构的全貌,全书别出心裁地按照RISC-V模块化的指令来组织内容,以帮助读者深刻理解RISC-V的关键特性, 本书值得每一位对RISC-V感兴趣的读者精读,并可作为从业者随时翻阅的案头参考书。 RISC-V 的基本概念和设计原则 深入分析RISC-V 的指令集、寄存器、内存管理、异常处理等 丰富的图表和示例 此外,本书还介绍x86、ARM 和MIPS 的设计,通过对比分析,突显RISC-V 的优势。 《RISC-V开放架构设计之道》由中科院计算所包云岗老师团队担纲翻译,是一本著译双馨的上乘佳作。

内容简介

本书首先提出一款指令集的7个评价指标,包括成本、简洁、性能、架构和实现分离、提升空间、代码大小、易于编程/编译/链接,并围绕这7 个评价指标从全系统角度向读者介绍RISC-V 的精巧设计和众多的取舍考量。同时,本书还介绍x86、ARM 和MIPS 的设计,并通过插入排序和DAXPY(双精度乘加)程序量化对比它们,突出RISC-V 的优势,深入阐释指令集设计对计算机系统的影响。 如果您是学生,本书将是一本优秀的课外读物,有助于您建立完整的计算机系统观念;如果您是教师,本书将为您提供丰富的真实案例,能给您的教学工作带来新的启发;如果您是相关方向的从业人士,本书除了开拓您的视野,还是一本方便的参考手册,帮助您更轻松地完成工作。

目录

作者简介

大卫·帕特森(David Patterson)在加州大学伯克利分校担任计算机科学系教授40 年,于2016 年退休,并加入“Google 大脑”项目担任杰出工程师。他还担任RISC-V 国际基金会董事会副主席和RISC-V 国际开源实验室主任。他曾被任命为伯克利计算机科学部主席,并当选计算研究协会(CRA,Computing Research Association)主席和计算机协会(ACM,Association for Computing Machinery)主席。在20 世纪80年代,他领导了四代精简指令集计算机(RISC,Reduced InstructionSet Computer)项目,伯克利*新的RISC 因此得名“RISC Five”(第五代RISC)。他和安德鲁·沃特曼(AndrewWaterman)均为四位RISC-V 架构师中的一员。安德鲁·沃特曼(Andrew Waterman),SiFive 的总工程师和联合创始人。SiFive 由RISC-V 架构的发明者们创办,旨在提供基于RISC-V 的低成本定制芯片。他获加州大学伯克利分校计算机科学博士学位。其间,他厌倦了现有指令集架构的变幻莫测,于是参与设计了RISC-V ISA 和**款RISC-V微处理器。安德鲁在多个开源项目中均做出主要贡献,包括基于RISC-V 指令集的开源Rocket chip 生成器、Chisel 硬件构造语言,以及Linux 操作系统内核、GNU C 编译器和C 库的RISC-V 版本移植工作。他还获加州大学伯克利分校硕士学位,期间开展了RISC-V 压缩扩展的前期工作。他还获杜克大学工学学士学位。包云岗,中国科学院计算技术研究所副所长、研究员,中国科学院大学计算机学院副院长,担任中国开放指令生态(RISC-V)联盟秘书长、RISC-V国际基金会理事会成员、中国计算机学会CCF开源发展委员会副主任。研究方向是计算机体系结构,包括芯片敏捷设计、数据中心体系结构等。先后开展访存监测设备HMTT、I/O访存DMA Cache、多核基准测试集PARSEC 3.0、标签化体系结构LvNA等前沿技术研究与原型系统研制,相关技术在华为、阿里、英特尔、微软等企业得到应用。近年来带领团队在国内率先开展了一系列开源芯片实践,包括开源高性能RISC-V处理器核“香山”项目、“一生一芯”计划、芯片敏捷设计云平台SERVE等,成为开源处理器芯片方向国际上主要科研团队之一。发表70余篇学术论文,包括ASPLOS、CACM、HPCA、ISCA、SIGCOMM、NSDI等国内外一流学术会议与期刊。曾获“CCF-IEEE CS”青年科学家奖、北京市“*美科技工作者”、共青团中央“全国向上向善好青年”等荣誉称号。

-

写给小白的Python入门实战课

¥16.0¥50.0 -

Photoshop图像处理标准培训教程

¥20.4¥68.0 -

翻转世界-互联网思维与新技术如何改变未来

¥16.0¥49.9 -

Excel 实战应用大全

¥15.9¥49.8 -

多功能智能机器小车的开发与研制

¥17.9¥56.0 -

APP INVENTOR少儿趣味编程动手做

¥18.9¥59.0 -

像数据达人一样思考和沟通:数据科学、统计学与机器学习极简入门

¥48.3¥68.0 -

造神:人工智能神话的起源和破除 (精装)

¥48.4¥88.0 -

全图解零基础word excel ppt 应用教程

¥14.4¥48.0 -

ABAQUS 6.14超级学习手册

¥78.5¥109.0 -

物联网关键技术及其数据处理研究

¥19.1¥59.8 -

Java编程思想{英文版·第四版}

¥72.3¥99.0 -

欧姆龙PLC编程及应用实例

¥41.8¥58.0 -

Word/Excel/PPT高效商务办公从入门到精通

¥15.4¥48.0 -

浪潮之巅 第4版(2册)

¥80.6¥139.0 -

Python数据爬取技术与实战手册

¥22.7¥59.8 -

HTML & CSS设计与构建网站

¥43.9¥79.8 -

机器学习导论

¥47.4¥79.0 -

flash经典课堂动画、游戏与多媒体制作案例教程

¥54.5¥99.0 -

Photoshop CS图像处理技术

¥25.2¥36.0