暂无评论

图文详情

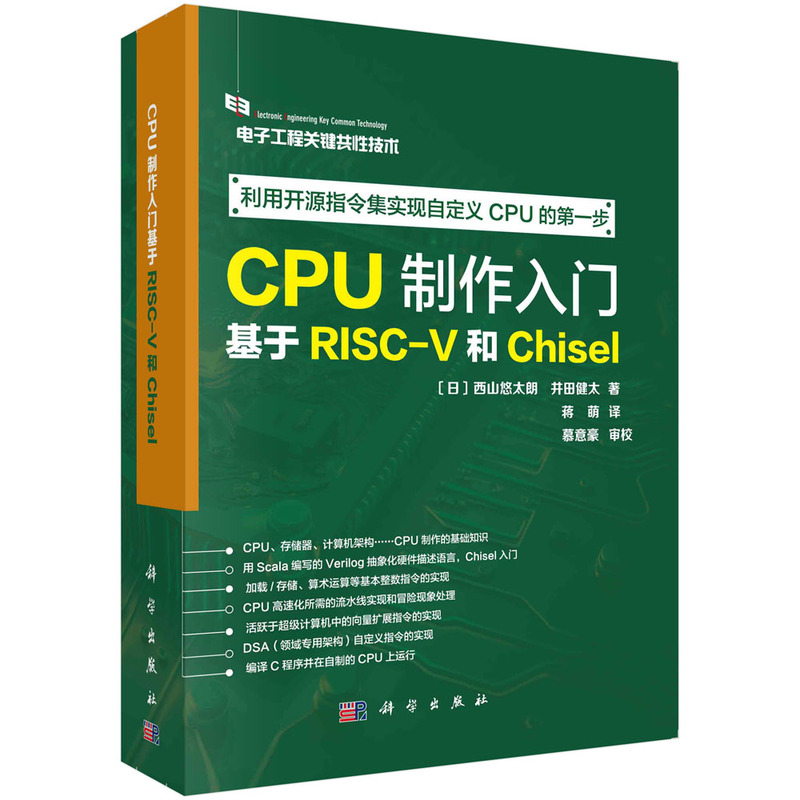

- ISBN:9787030769657

- 装帧:平装胶订

- 册数:暂无

- 重量:暂无

- 开本:其他

- 页数:344

- 出版时间:2024-01-01

- 条形码:9787030769657 ; 978-7-03-076965-7

内容简介

本书基于RISC-V和Chisel讲解自定义CPU的实现。全书分为5个部分,立足于CPU、存储器、计算机架构等基础知识,逐步带领读者实现简单的加减法、分支、比较等基础指令,理解流水线对于CPU高速化的重要意义及实现,*后应用向量扩展语言实现自定义CPU。要提醒的是,本书所指的“CPU制作”仅限于软件上的设计和模拟,不涉及FPGA上的实现。

目录

目录

第Ⅰ部分 CPU制作的基础知识

第1章什么是CPU 2

1.1 电路能够描述逻辑的理由 3

1.1.1 转换为数字信号 3

1.1.2 描述逻辑运算的电路 4

1.1.3 可以描述任何真值表的基本逻辑电路 7

1.2 为何能用基本逻辑电路实现CPU 9

1.2.1 时序逻辑电路:锁存器 10

1.2.2 有限状态机 11

1.2.3 通过时钟信号同步 13

1.3 CPU的制造流程 17

第2章计算机架构 19

2.1 存储器 20

2.1.1 寄存器 21

2.1.2 主存 21

2.2 计算机的基本处理流程 22

2.2.1 取指令(IF) 23

2.2.2 指令译码(ID) 23

2.2.3 运算(EX)27

2.2.4 访存(MEM) 27

CPU制作入门:基于RISC-V和Chisel

2.2.5 回写 27

第3章 Chisel基础 30

3.1 什么是Chisel 31

3.2 什么是面向对象 32

3.2.1 类和实例 32

3.2.2 继承 33

3.3 Scala的基本语法 34

3.3.1 变量var和val 35

3.3.2 方法:def() 35

3.3.3 集合:Seq 35

3.3.4 for表达式 36

3.3.5 对象 37

3.3.6 命名空间 40

3.4 Chisel的基本语法 42

3.4.1 位值的基本类型 42

3.4.2 运算符 44

3.4.3 Module类 47

3.4.4 IO对象 48

3.4.5 Flipped对象 49

3.4.6 信号连接 50

3.4.7 组合逻辑电路:Wire/WireDefault 51

3.4.8 时序逻辑电路:RegInit 51

3.4.9 用Mem定义寄存器文件 52

3.4.10 控制电路 52

3.4.11 位操作 56

3.4.12 用printf调试 57

第Ⅱ部分简单的CPU实现

第4章环境架构 60

4.1 下载chisel-template 60

4.2 用Docker架构运行环境 61

4.2.1 安装Docker 61

4.2.2 创建Dockerfile 61

4.2.3 创建镜像 62

4.2.4 创建容器 63

4.3 指令位列和常量文件 63

4.3.1 Instructions.scala 64

4.3.2 Consts.scala 66

4.4 第Ⅱ部分要实现的指令和Chisel完整代码 69

第5章取指令的实现 76

5.1 Chisel代码概要 76

5.2 Chisel的实现 77

第6章用ChiselTest进行取指令测试 80

6.1 ChiselTest的实现 80

6.2 测试流程 81

6.3 创建Chisel测试代码 81

6.3.1 特征:trait 82

6.3.2 peek() 方法 83

6.3.3 clock.step() 方法 83

6.4 创建存储器用HEX文件 83

6.5 用printf输出调试信号 85

6.6 运行测试 85

6.7 Docker容器的commit 86

第7章指令译码器的实现 87

7.1 Chisel的实现 87

7.1.1 寄存器编号的译码 87

7.1.2 寄存器数据的读取 87

7.1.3 调试信号的输出 88

7.2 运行测试 88

第8章 LW指令的实现 90

8.1 RISC-V的LW指令定义 90

8.2 Chisel的实现 91

8.2.1 指令位模式的定义 92

8.2.2 CPU和存储器之间的端口定义 93

8.2.3 CPU内部的处理实现 94

8.2.4 存储器的数据读取实现 95

8.3 运行测试 96

8.3.1 创建指令文件lw.hex96

8.3.2 存储器加载文件名的修改 97

8.3.3 测试结束条件的修改 97

8.3.4 添加调试信号 97

8.3.5 运行测试 98

第9章 SW指令的实现 99

9.1 RISC-V的SW指令定义 99

9.2 Chisel的实现 100

9.2.1 指令位模式的定义 101

9.2.2 CPU和存储器间的端口定义 101

9.2.3 CPU内部的处理实现 101

9.2.4 存储器的数据写入实现 102

9.3 运行测试 102

9.3.1 创建指令文件sw.hex 102

9.3.2 存储器加载文件名的修改 104

9.3.3 测试结束条件的修改 104

9.3.4 添加调试信号 104

9.3.5 运行测试 104

第10章加减法指令的实现 106

10.1 RISC-V的加减法指令定义 106

10.2 Chisel的实现 107

10.2.1 指令位模式的定义 107

10.2.2 加减法结果的连接(EX阶段) 107

10.2.3 加减法结果的寄存器回写(WB阶段) 108

第11章逻辑运算的实现 109

11.1 RISC-V的逻辑运算指令定义 109

11.2 Chisel的实现 110

11.2.1 指令位模式的定义 110

11.2.2 逻辑运算结果的连接(EX阶段) 111

11.2.3 逻辑运算结果的寄存器回写(WB阶段) 111

第12章译码器的强化 112

12.1 ALU译码 112

12.1.1 译码器的强化(ID阶段) 112

12.1.2 利用译码信号简化ALU(EX阶段) 113

12.2 MEM译码 114

12.2.1 译码器的强化(ID阶段) 114

12.2.2 指令译码的非必要化(MEM阶段) 115

12.3 WB译码 115

12.3.1 译码器强化(ID阶段) 116

12.3.2 指令译码的非必要化(WB阶段) 116

第13章移位运算的实现 118

13.1 RISC-V的移位运算指令定义 118

13.2 Chisel的实现 119

13.2.1 指令位模式的定义 119

13.2.2 译码信号的生成(ID阶段) 120

13.2.3 移位运算结果的连接(EX阶段) 120

第14章比较运算的实现 121

14.1 RISC-V的比较运算指令定义 121

14.2 Chisel的实现 122

14.2.1 指令位模式的定义 122

14.2.2 译码信号的生成(ID阶段) 122

14.2.3 比较运算结果的连接(EX阶段) 123

第15章分支指令的实现 124

15.1 RISC-V的分支指令定义 124

15.2 Chisel的实现 126

15.2.1 指令位模式的定义 126

15.2.2 PC的控制(IF阶段) 126

15.2.3 立即数和译码信号的生成(ID阶段) 127

15.2.4 分支可否、跳转目标地址的计算(EX阶段) 128

第16章跳转指令的实现 129

16.1 RISC-V的跳转指令定义 129

16.2 Chisel的实现 131

16.2.1 指令位模式的定义 131

16.2.2 译码和操作数数据的读取(ID阶段) 131

16.2.3 添加JALR运算(EX阶段) 132

16.2.4 PC的控制(IF阶段) 132

16.2.5 ra的回写(WB阶段) 133

第17章立即数加载指令的实现 134

17.1 RISC-V的立即数加载指令定义 134

17.2 Chisel的实现 135

17.2.1 指令位模式的定义 135

17.2.2 译码和操作数数据的读取(ID阶段) 136

第18章 CSR指令的实现 138

18.1 RISC-V的CSR指令定义 138

18.2 Chisel的实现 141

18.2.1 指令位模式的定义 141

18.2.2 立即数和译码信号的生成(ID阶段) 141

18.2.3 op1_data的连接(EX阶段) 142

18.2.4 CSR的读写(MEM阶段) 142

18.2.5 CSR读取数据的寄存器回写(WB阶段) 143

第19章 ECALL的实现 144

19.1 RISC-V的ECALL指令定义 144

19.2 Chisel的实现 145

19.2.1 指令位模式的定义 145

xvi

CPU制作入门:基于RISC-V和Chisel

19.2.2 PC的控制(IF阶段) 145

19.2.3 译码信号的生成(ID阶段) 146

19.2.4 CSR写入(MEM阶段) 146

第20章用riscv-tests进行测试 147

20.1 riscv-tests的构建 147

20.2 将ELF文件转换为BIN文件 148

20.3 BIN文件的十六进制化 149

20.4 riscv-tests的路径条件 150

20.5 riscv-tests的执行 153

20.5.1 Chisel的实现 153

20.5.2 运行测试 154

20.6 批量测试脚本 156

20.6.1 HEX文件的批量生成:tohex.sh 156

20.6.2 riscv-tests的批量运行:riscv-tests.sh 156

第21章试运行C程序 159

21.1 创建C程序 159

21.2 编译 161

21.3 链接 163

21.4 机器语言的十六进制化和DUMP文件的创建 164

21.5 运行测试 165

第Ⅲ部分流水线的实现

第22章什么是流水线 168

22.1 流水线的意义 168

22.2 创建CPU流水线 170

22.3 在第Ⅲ部分完成的Chisel代码 170

第23章流水线寄存器的设置 179

23.1 寄存器的定义 179

23.2 IF阶段 181

23.2.1 取指令和PC控制 181

23.2.2 IF/ID寄存器的写入 181

23.3 ID阶段 182

23.3.1 寄存器编号的译码和寄存器数据的读取 182

23.3.2 立即数的译码 182

23.3.3 csignals的译码 182

23.3.4 操作数数据的选择 183

23.3.5 生成csr_addr 183

23.3.6 ID/EX寄存器的写入 183

23.4 EX阶段 184

23.4.1 至alu_out的信号连接 184

23.4.2 分支指令的处理 185

23.4.3 EX/MEM寄存器的写入 185

展开全部

本类五星书

本类畅销

-

乡村振兴新技术:新时代农村短视频编辑技术基础入门

¥12.8¥32.0 -

AI绘画+AI摄影+AI短视频从入门到精通

¥45.5¥79.8 -

企业AI之旅

¥43.5¥79.0 -

机器学习

¥59.4¥108.0 -

基于知识蒸馏的图像去雾技术

¥61.6¥88.0 -

软件设计的哲学(第2版)

¥51.0¥69.8 -

智能算法优化及其应用

¥52.4¥68.0 -

Photoshop图像处理

¥25.5¥49.0 -

R语言医学数据分析实践

¥72.3¥99.0 -

大模型推荐系统:算法原理、代码实战与案例分析

¥62.3¥89.0 -

剪映 从入门到精通

¥25.7¥59.8 -

游戏造梦师----游戏场景开发与设计

¥67.6¥98.0 -

SAR图像处理与检测

¥35.4¥49.8 -

人工智能

¥29.4¥42.0 -

中文版PHOTOSHOP 2024+AI修图入门教程

¥59.3¥79.0 -

WPS办公软件应用

¥25.2¥36.0 -

格拉斯曼流行学习及其在图像集分类中的应用

¥13.7¥28.0 -

轻松上手AIGC:如何更好地向CHATGPT提问

¥40.3¥62.0 -

元宇宙的理想与现实:数字科技大成的赋能与治理逻辑

¥61.6¥88.0 -

云原生安全:攻防与运营实战

¥66.8¥89.0